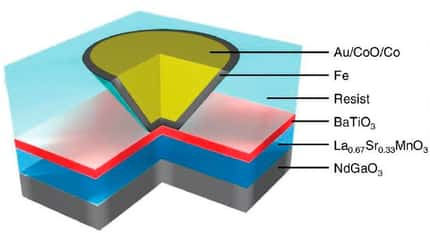

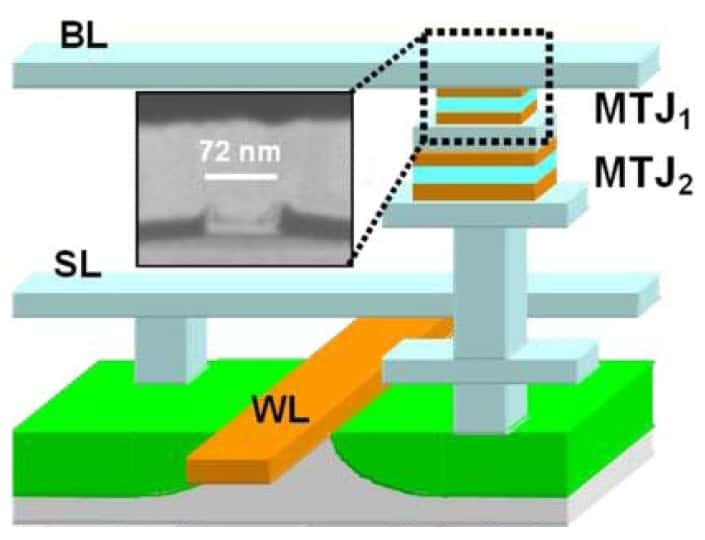

Schéma de la MRam MLC présentée par Hitachi et l'université Tohoku. Dans chaque cellule, commandée par les trois lignes habituelles (WL, Word Line ; BL, Bit Line ; SL, Source Line), se trouvent deux éléments MTJ1 et MTJ2 (Magnetic Tunnel Junction) contenant chacun un bit. L'un est plus petit que l'autre, ce qui conduit à des propriétés physiques différentes, permettant de les commander séparément. © Hitachi

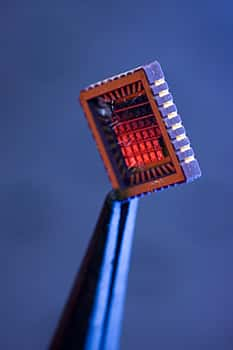

Résultats directs des progrès en matièrematière de spintronique, un domaine qui exploite le spinspin des électronsélectrons, c'est-à-dire leurs propriétés magnétiques, les MRam (Magnetic Random Access MemoryRandom Access Memory) font l'objet d'intenses recherches depuis de nombreuses années. Il est dit que ces mémoires, que l'on nomme aussi parfois SPRam (Spin-transfer Torque Ram) remplaceront un jour les actuelles DRam au moins dans les ordinateurs portables et autres objets baladeurs. On pense également à en faire des remplaçantes des mémoires Flash. Les MRam, en effet, ne nécessitent pas d'alimentation pour maintenir l'information qu'elles contiennent. Les problèmes techniques, cependant, ne manquent pas, venant notamment brider la capacité ou conduisant à des coûts de fabrication élevés.

Régulièrement, une entreprise ou un laboratoire annonce un progrès marquant. C'est de nouveau le cas : lors d'une conférence sur les circuits intégrés (2010 Symposium on VLSI Technology), Hitachi et l'université Tohoku ont détaillé le fonctionnement d'une mémoire MRam originale dans laquelle chaque cellule contient deux éléments TMR (Tunnel MagnetoResistance, magnétorésistancemagnétorésistance tunnel) montés en série. Comme toute mémoire magnétique, chacun de ces éléments mémorise deux états (0 ou 1, donc) caractérisés par les spins (l'orientation magnétique des électrons) au sein d'une double couche ferromagnétiqueferromagnétique enserrant un isolant. Dans un tel sandwich, la résistance électriquerésistance électrique dépend fortement du champ magnétiquechamp magnétique, donc de l'état magnétique des couches ferromagnétiques. C'est la magnétorésistance, qualifiée de tunnel car elle déclenche des courants d'électrons par effet tunneleffet tunnel.

Plus dense, moins chère mais plus lente ?

Empilés l'un sur l'autre dans la même cellule, donc au sein d'un même dispositif de lecture-écriture, les deux éléments TMR devraient avoir la fâcheuse tendance de se comporter comme un seul, l'enregistrement d'un 0 ou d'un 1 s'effectuant sur les deux simultanément. De même, la lecture d'un des éléments ne pourrait différencier l'un de l'autre. Pour y parvenir, les concepteurs de cette SPRam MLC (MLC pour Multi-Level Cell) ont recouru à une astuce : l'un des éléments TMR est plus petit que l'autre, ce qui induit des propriétés différentes (courant de seuil pour l'écriture et variation de résistance pour la lecture). Les ingénieurs nippons disent parvenir ainsi à utiliser séparément les deux éléments.

Pourquoi tant d'efforts pour réunir ainsi deux bits (donc quatre valeurs possibles) dans une même cellule mémoire ? Pour en réduire la taille ou, à l'inverse, augmenter la capacité à surface de circuit égale. Comme le procédé de fabrication n'est pas deux fois plus complexe, le prix de revient au bit est diminué aussi. Mieux, les ingénieurs à l'origine de l'annonce affirment pouvoir réaliser des cellules à trois éléments, qui pourront donc engranger un nombre à trois bits, soit huit en tout, entre 0 et 7. De quoi réduire encore le coût et la taille...

En revanche, le principe risque de faire grimper les temps d'écriture et de lecture. Ce ralentissement - drastique - s'observe également sur les mémoires Flash, les fabricants ayant là aussi essayé les versions MLC, que l'on trouve aujourd'hui dans des disques SSD.