au sommaire

Il y aurait un « murmur de la mémoire », explique la communication de MicronMicron, un fabricant américain de composants électroniques. Alors que les performances des processeurs ne cessent de progresser, la vitessevitesse des mémoires vives (DDRam puis DDR 2 puis DDR 3) n'augmenterait plus assez, jusqu'à constituer le goulet d'étranglement de l'électronique actuelle et mettre en défaut la loi de Moore.

Au début de l'année, Micron avait décrit - succinctement - un circuit mémoire baptisé HMC, pour Hybrid Memory Cube, qui permettrait des progrès drastiques en matièrematière de vitesse, c'est-à-dire de débit des données (ou bande passante) entre la mémoire et le processeur : il serait « 15 fois supérieur à celui de la DDR 3 », tout en consommant « 70 % de moins ». Aucun chiffre n'est donné en valeur absolue. Or, le débit des DDR 3 est variable selon la fréquence de fonctionnement : en 800 MHz, il est de 6,4 Go/s et de 12,8 Go/s en 1.600 MHz. Il n'est pas dit quelle valeur doit être multipliée par 15. Il est clair que le HMC n'est aujourd'hui qu'un nouveau procédé, à finaliser, et qu'il s'apprête à inaugurer une famille de circuits.

SamsungSamsung, convaincu de l'intérêt de la formule, vient de créer un consortium avec Micron (HMCC) pour accélérer l'industrialisation de ces circuits. La finalisation des caractéristiques est annoncée pour 2012 et la commercialisation espérée en 2014 ou 2015.

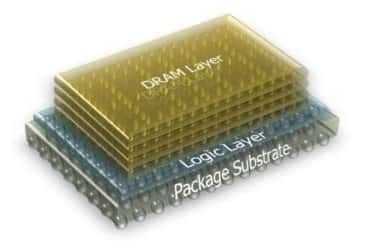

Dans une puce HMC, les cellules mémoire (DRAM Layer, couche DRam) sont installées sur le circuit assurant le contrôle (Logic Layer, couche logique). C'est cette partie qui recueille les demandes du processeur (« donne-moi le contenu de la mémoire numéro tant » ou « range-moi cette valeur dans la mémoire numéro tant »). La couche inférieure (Packaqe substrate) schématise le support physique du circuit. © Micron

La troisième dimension en électronique

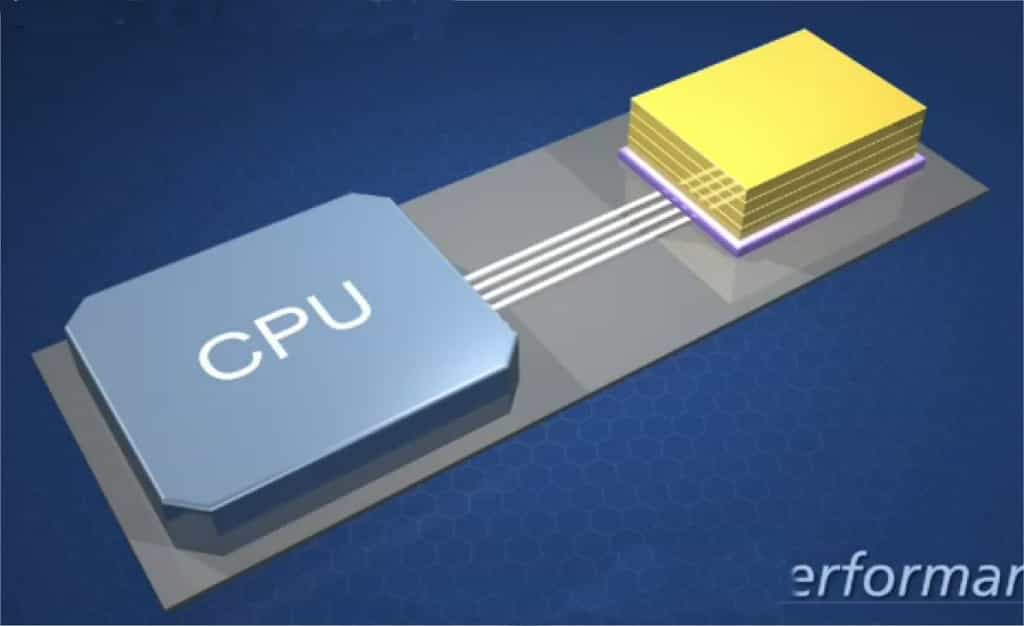

Pour parvenir à ces performances, Micron a construit un circuit à deux étages. La zone occupée par les cellules mémoire se trouve juchée sur celle abritant le circuit de contrôle logique. D'ordinaire, celui-ci est installé sur un composant séparé. D'où le nom d'hybridehybride donné au HMC. On obtient donc logiquement un évident gain de surface mais aussi une plus grande vitesse de travail.

Ce n'est pas la première fois que les ingénieurs de l'électronique explorent la troisième dimension, alors que les circuits actuels s'étalent en deux dimensions. Les difficultés de réalisation ont toujours limité les succès de la démarche mais les concepteurs de circuits sont gens tenaces et les technologies progressant, ce qui était impossible hier devient difficile aujourd'hui et sera sans doute banal demain (puis obsolète après-demain).

IntelIntel avait montré des « puces 3D » en mai dernier, en l'occurrence des transistors baptisés Tri-Gate (triple porteporte). Il ne s'agissait donc pas de circuits mémoire complets mais, à une échelle bien plus petite, du composant de base de l'électronique, assurant aussi le fonctionnement du processeur. On ne sait pas encore comment cette troisième dimension sera exploitée dans les décennies à venir mais on commence déjà à voir se concrétiser les premières pistes...