au sommaire

Depuis des années, les informaticiens cherchent à contourner le goulot d'étranglementgoulot d'étranglement entre processeur et mémoire. Le premier travaille de plus en plus vite et, de plus, a besoin d'avaler toujours plus de données, alors que la vitessevitesse d'échange avec les circuits mémoire ne progresse que peu. Résultat, les processeurs du monde entier passent une grande partie de leur vie à attendre... Mémoires caches, multithreading ou pipeline ont fait une partie du chemin mais les chercheurs veulent aller plus loin avec des « architectures non-Von Neumann », c'est-à-dire différentes de celle adoptée pour nos ordinateurs depuis plus d'un demi-siècle.

L'idée en vogue est d'effectuer tout ou partie des calculs directement dans la mémoire. Il est par exemple possible d'installer des petites unités de calcul au sein des circuits de mémoire. C'est l'approche PIM, pour Processing-in-memory. Une autre voie est celle des puces neuromorphiques, visant à s'inspirer des réseaux de neuronesneurones animaux, comme le récent Loihi d’Intel, encore expérimental. Le cas dont nous parlons ici est celui de l'IMCIMC, pour In-memory computing (on remarquera que les termes français sont à peu près inexistants). Son principe est de faire exécuter des calculs par les mémoires elles-mêmes, avec un fort parallélisme, une même opération étant réalisée simultanément sur un grand nombre de données.

Le saviez-vous ?

« L’architecture de von Neumann » désigne celle des ordinateurs tels qu’ils sont fabriqués aujourd’hui. Attribuée à John von Neumann, mathématicien et physicien, elle se compose de quatre composants :

- la mémoire, qui contient à la fois les instructions du programme à exécuter et les données qui seront traitées,

- l’unité de contrôle, qui exécute les instructions,

- l’unité arithmétique et logique, qui réalise les calculs et les tests d’égalité,

- l’interface avec le monde extérieur (clavier, imprimante, écran…).

Avec l’amélioration de réalisation des circuits, la vitesse de travail du processeur (qui enferme l’unité de contrôle et l’unité arithmétique et logique) a augmenté beaucoup plus que celle des transferts vers ou depuis la mémoire. Ce hiatus a été baptisé « goulot d’étranglement de von Neumann ».

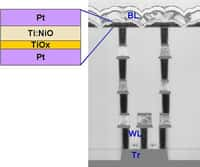

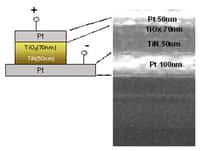

Au laboratoire IBMIBM Research de Zürich (Suisse), Manuel Le Gallo travaille sur les mémoires résistives à changement de phase, ou PCM (Phase Change Memory). En fonction de la tension appliquée, leur matériaumatériau change de structure, entre deux états, cristallin ou amorpheamorphe. La résistance électriquerésistance électrique de ce dernier étant plus élevée, une même tension produira ensuite un courant d'intensité différente.

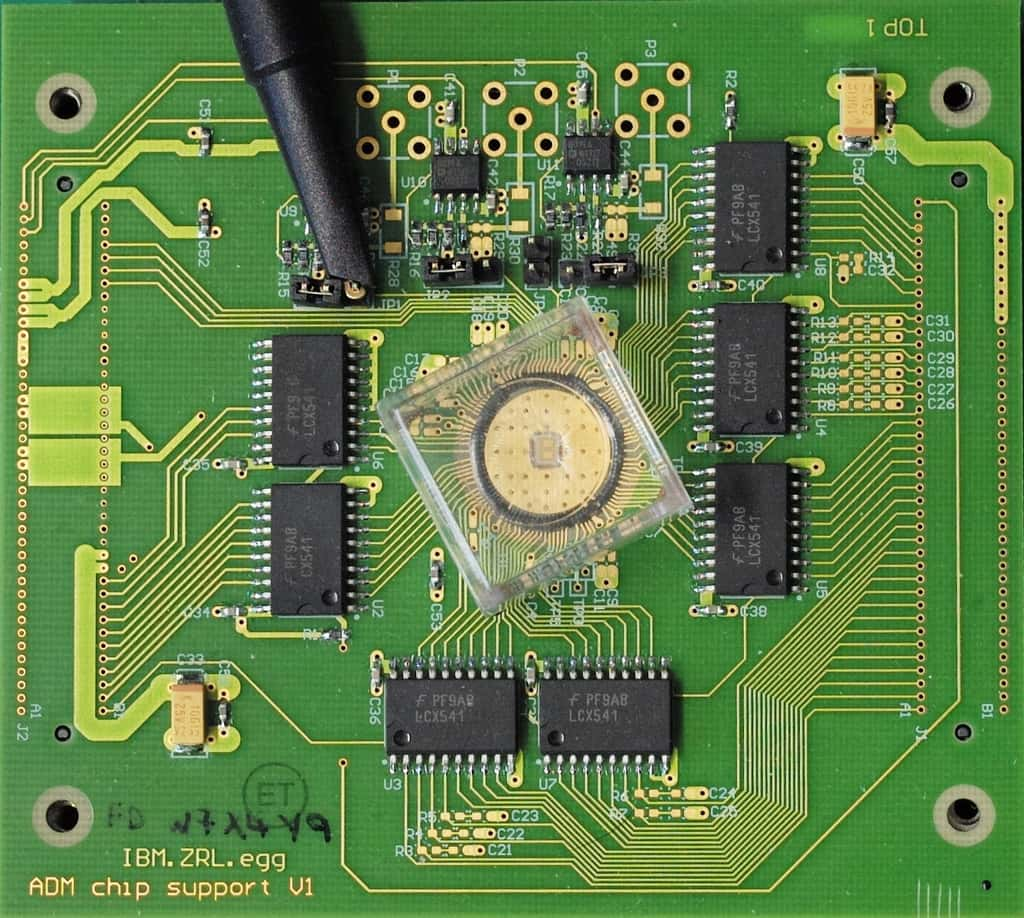

« Dans notre circuit, nous encodons les données dans des mémoires PCM gérées comme une matrice de lignes et de colonnes. Nous appliquons une variation de tension sur toute une ligne et les courants sortants représentent le résultat de l'opération. C'est donc un calcul analogiqueanalogique, explique Manuel Le Gallo. Il serait possible d'opérer également des DRam classiques de façon analogique mais, alors, le contenu des mémoires serait effacé après un temps relativement court, de l'ordre de dix millisecondes. »

Le circuit expérimental avec la mémoire résistive à changement de phase, au centre. © IBM Research Zürich

Un calcul à précision mixte, entre analogique et numérique

D'où les mémoires résistives. Mais ce mode analogique a un défaut énorme : le résultat est très peu précis. « Avec des DRam numériquesnumériques, les nombres en virgule flottante peuvent être encodés sur 32 ou 64 bits. Avec des mémoires résistives analogiques, la précision effective est d'environ quatre bits... » Le travail de l'équipe de Zürich a consisté à hybrider un tel circuit avec un processeur classique, qui calcule en numérique, et à imaginer un concept, nouveau, d'une « précision mixte ». Ainsi ont-ils nommé leur procédé. Les chercheurs ont mis au point un algorithme itératif exploitant les deux modes : le calcul est d'abord réalisé par les PCM, avec un résultat approximatif, puis affiné avec un calcul numérique. L'opération est répétée plusieurs fois, la précision étant augmentée à chaque étape.

Pour tester cette idée, l'équipe a travaillé sur un ensemble d'équationséquations linéaires et des données réelles, en l'occurrence des mesures d'expression par ARNARN de 40 gènesgènes obtenues chez des patients atteints de cancerscancers. « 80 % des problèmes à résoudre en sciences ou en ingénierie peuvent être formulés en tant que systèmes d'équations linéaires. »

“L'étape suivante sera le Deep learning”

Publiée dans la revue Nature Electronics en avril 2018, la description de la méthode et les résultats montrent que l'idée était bonne. « La mémoire dans laquelle nous avons encodé ces données comportait 512 x 2.048 unités, à peu près un million, donc. C'est peu pour résoudre des problèmes à grande échelle mais elle nous a servi de démonstrateurdémonstrateur. » Globalement, l'efficacité du principe de « précision mixte » a été démontrée. Il conduit à une réduction notable du nombre de calculs effectués dans le processeur, et donc de la consommation électrique. D'après l'équipe, le gain d'efficacité énergétique serait important, « 80 fois celui d'une solution comparable utilisant des circuits CMos à faible précision ».

Pour les chercheurs d'IBM, l'étape suivante sera d'utiliser un dispositif de taille plus grande et non plus pour des équations linéaires « mais sur du Deep learningDeep learning ». L'objectif, en effet, n'est pas de remplacer l'architecture traditionnelle d'un ordinateur par une autre mais de construire des coprocesseurscoprocesseurs avec ces circuits à PCM, qui seraient chargés de certains calculs sur des quantités massives de données.

Ce qu’il faut

retenir

- Des architectures dites « non-von Neumann » sont recherchées pour accélérer la vitesse des ordinateurs.

- Elles conduisent à effectuer une partie des calculs dans la mémoire vive.

- Une voie est celle d'opérations analogiques, réalisées par addition de courant dans des mémoires PCM, à résistance variable.

- Ici, il a été démontré la validité du concept de « précision mixte », exploitant le calcul analogique, peu précis, en conjugaison avec le calcul numérique classique.